Enhavtabelo

UDIMM vs DIMM

Ĉu estus malĝuste diri, ke en ĉi tiu rapida kaj teĥnik-impregnita mondo, multaj homoj fakte ne konscias pri komputilaj memoraj agordoj? Verŝajne.

Por multaj uzantoj, dum la tekniko faras la laboron, ili estas feliĉaj. Sed se vi volas kompreni iom pli pri kiel funkcias teknologio, kien vi povas serĉi?

Nu, vi estas en la ĝusta loko. Do, ĉu vi volas lerni pri DIMM (duobla en-linia memormodulo) ?

DIMM estas integrita en la memorfendojn de la ĉeftabulo. Ili povas esti nomitaj RAM-bastonoj aŭ UDIMM ankaŭ.

DIMM estas konsistita de dinamikaj RAM-integraj cirkvitoj sur la cirkvitotabulo . DIMM estas regule uzata por personaj kaj laborejkomputiloj , krom serviloj.

Kun la lanĉo de la Pentium-procesoro de Intel, SIMM-oj estis anstataŭigitaj per DIMM-oj . Ofte, SIMM (ununura enlinia memormodulo) estas nomita la antaŭulo de DIMM.

SIMM-oj havis redundajn kontaktojn ambaŭflanke, dum DIMM estas unike dizajnita kun aparta elektra kontakto sur ĉiu el la moduloj. .

DIMM-oj estas dizajnitaj kun 64-bita datumplano kontraste al la 32-bita datumvojo de sia antaŭulo. Kun la apero de la Pentium-procesoro, ekestis la bezono de kongrua par-integriĝo de 64-bita busa larĝo, sed SIMM-oj ne estis kapablaj elteni tion.

Sekve, DIMM-oj estis kreitaj por plenumi ĉi tion. postulo . Enkrome, la 64-bita datumvojo certigis pli rapidan datumtraktadon kaj transdonon de datumoj kompare kun tiu ofertita de SIMM.

Dum la jaroj, DIMM fariĝis la norma formo de komputilo. memoro . DIMM estas instalita sur la baztabulo kaj stokas informojn en malsamaj memorĉeloj .

UDIMM kontraŭ DIMM

Dum jaroj teknikaj geeks scivolis kiel UDIMM kaj DIMM estas rilataj.

DIMM estas esence la duobla en-linia memormodulo kiu estas la neregistrita memora agordo .

Krome, DIMM estas kutime nomata "konvencia". memoro.' Nun, ekzistas kvar bazaj specoj de DIMM tie:

- UDIMM – neregistrita kaj nebufrita memoro

- RDIMM – registrita memoro

- SO-DIMM - la baza tekokomputila RAM

- FBDIMM - plene bufrita memoro

UDIMM estas la normala RAM kaj nebufrita DIMM. Ĉi tiu estas la memorpeto vaste uzata en tekkomputiloj kaj labortablaj komputiloj.

Ĉi tiuj UDIMM-oj ofertas pli rapidan rendimenton. Ĉi tiu memora agordo havas sufiĉe prezon, sed povus esti kompromiso pri stabileco.

Por pli bonaj komprenoj, ni desegnis ĉi tiun artikolon, kiel tia:

- dividado de informoj pri DIMM,

- ĝia arkitekturo,

- kaj kiom malsamaj faktoroj povas influi la latentecon de via komputila memoro.

Ĉu ni komencu?

Trajto 1: Arkitekturo de DIMM

Kiel ni jam menciis, DIMM estas lapresita cirkvito integrita kun SDRAM kaj aŭ DRAM integraj cirkvitoj.

Tamen estas aliaj komponantoj, kiuj influas la agadon kaj skizas la funkciecon de DIMM. Bonvolu legi plu por lerni pri ĝiaj trajtoj.

Trajto 2: Malvarmigo

La denseco de la blato estis esence pliigita por plibonigi la agadonormojn , promesante pli bonan generacion de horloĝrapideco sed ankaŭ pli da varmo.

Antaŭe oni uzis 16GB kaj 8GB blatojn, sed ili ne optimumigis la varmegan disvolviĝon.

Tamen, kiam la blato denseco estis plifortigita al 64GB, la redukto de varmo fariĝis decida .

Teknikaj fabrikantoj evoluigis varmoreduktajn teknologiojn por helpi minimumigi la varmegon de DIMM-oj.

Malvarmigaj naĝiloj estis inkluzivitaj por troa varmo-elfluo. La varmo estis eligita el la ĉeftabulo en la elirvojon de komputiloj.

Trajto 3: Memoraj Rangoj

La plej novaj DIMM-oj estis dizajnitaj per sendependaj DRAM-pecetaroj , ankaŭ konataj kiel memoraj rangoj .

Ĉi tiuj rangoj kondukas al DRAM-paĝa inico, kiu produktas. pli bona rendimentoprocento.

Estas sufiĉe klare, ke rangoj estas konektitaj al simila adreso dum kreado de densa memoro por la procesoroj. Kontraste, la procesoroj ne aliras la rangojn por identaj operacioj.

Procesoroj estas povigitaj per interplektado kiu helpas uzi larangoj per malsamaj operacioj.

La uzantoj povas skribi al unu rango, sed legado estos el alia ellasejo.

Post kompletiĝo de operacioj, DRAM forigas la datumojn . En ĉi tiu vico, unuopaj kanaloj povas kaŭzi halton en la duktoj.

Trajto 4: Kanala Memoro

Kiam temas pri DIMM , unukanala memoro estas la minimuma antaŭkondiĉo por komunikado kun la procesoro.

Konsekvence, la 64-bitaj kanaloj estas desegnitaj per dukanala memoro , xx” por la kvarkanala kaj xx por la trikanala.

Sed estas esence skizi, ke DIMM-teknologio ne signalas plurkanalan memoron.

Trajto 5: SDR SDRAM

La signala datumrapideco de DIMM estis desegnita jam en la 1960-aj jaroj. En ĉi tiu kazo, rapideco kaj efikeco estas mezuritaj en nanosekundoj .

DRAM-rapidecoj estas plifortigitaj per SDRAM, prezentante sinkronigajn ŝanĝojn al la horloĝtempo en la CPU.

Ĉi tiu teknologio tendencas aktivigi rapide dum determinas la precizan tempon por datumtraktado .

Tamen estas nul prokrastoj por CPU-prilaborado .

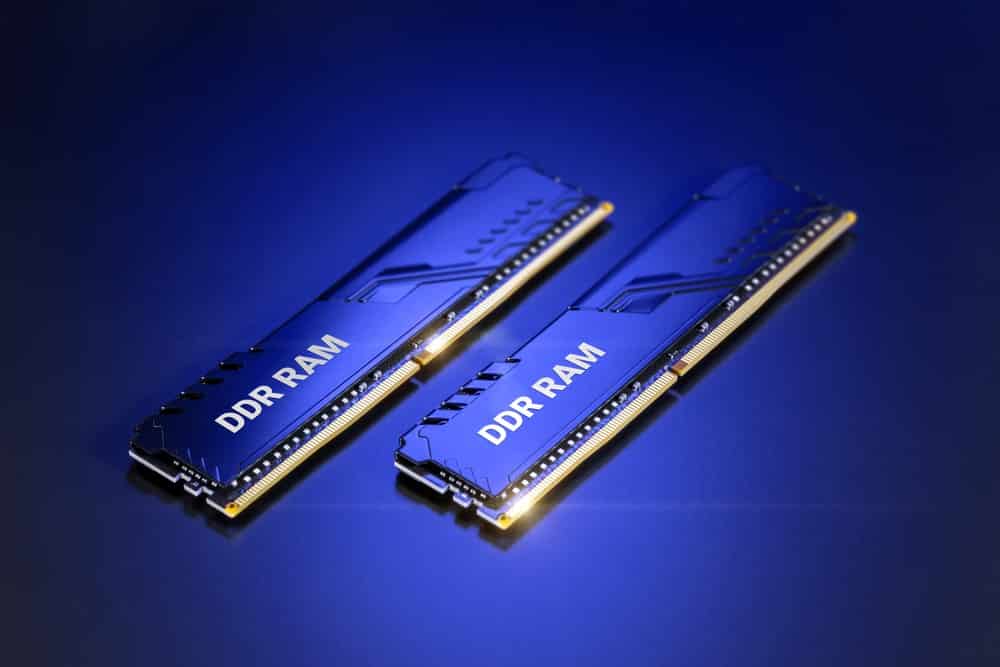

Trajto 6: DDR-Generacioj

Estas 4 generacioj de DIMM kaj DDR - DDR, DDR3, DDR2, kaj DDR4.

- La DDR2. estis desegnita por akceli la transigan indicon dum bufro de la unua generacio .

- DDR3 helpas plibonigi rendimenton dum pozado.redukto de energikonsumo .

- Laste sed ne malplej, DDR4 ne nur reduktas la tension sed plibonigas la rendimenton kaj transigan indicon .

Moviĝante al la DIMM-oj, ekzistas unuopaj rangoj desegnitaj kun alta kapablo.

Aliflanke, procesoroj paraleligos rangomodulojn kaj memorpetojn.

En la suba sekcio, ni aldonis multoblajn faktorojn, kiuj povas influi la memoran latentecon per DIMM en komputila sistemo . Rigardu!

Trajto 7: Rapido

Kun rapida DIMM-rapideco, la latencia indico estos pli malalta, kondukante al ŝarĝita latenco.

Vidu ankaŭ: 6 Manieroj Ripari Eraron de Comcast XRE-03121La latencia indico pliiĝas kiam memorpetoj estas sendataj konstante, restante forta por ekzekuto .

Pli rapidaj DMM-rapidoj kondukas al rapida memorkontrolo . Kun tiaj rapidoj, vicigitaj komandoj estas procesitaj rapide.

Trajto 8: Rangoj

Kun DIMM kaj DDR4 memorrapideco, la ŝarĝita latenco pliiĝas laŭ la rangoj.

Pli alta rangorapido produktas pli grandan kapablon por prilabori memorpetojn .

Krome ĝi helpas redukti la peton. vostovicoj dum plibonigas la kapablon kontroli la refreŝigajn komandojn .

Tamen ĝi emas redukti la ŝarĝitan latentecon per multoblaj rangoj. Kiam la kanalo vicas. estas pliigitaj de kvar, ŝarĝita latenteco pliiĝas.

Trajto 9: CAS

CAS estas desegnita kiel la kolumna adreso strobo, kiu tendencas reprezenti la DRAM-respondtempon.

La nombro da horloĝcikloj estas specifita, kiel 13, 15, kaj 17.

La kolumnadreso estas desegnita sur la buso sed malŝarĝis kaj ŝargis latenciajn mezurojn. .

Trajto 10: Utiligo

La memorbusa utiligo, kiam pligrandiĝas, malpli verŝajne ŝanĝas la malaltan legan nivelon de latenteco.

Tio ĉi estas reduktita sur la memorbuso. Uzantoj devas skribi kaj legi la komandojn permane.

Vidu ankaŭ: Linksys RE6300 Ne Funkcias: 4 Manieroj RipariTamen, la sama tempo estas bezonata por plenumi ĉi tiujn komandojn , sendepende de la volumo de trafiko.

Kiam la utiligo pliiĝas, la latenteco de la memorsistemo pliiĝas ĉar vicoj estas plenplenaj kun la latenteco, korpigita en la memorregilon.